# Realização em tecnologia monolítica de Arsenieto de Gálio (GaAs MMIC) de amplificadores sintonizados para recuperação de relógio a 10 e 20 Gbps\*

António L.J. Teixeira, Mário J. N. Lima, J. Nuno Matos, Paulo Monteiro, J. R. Ferreira da Rocha

Resumo - Actualmente os recuperadores de relógio para frequências superiores a 10 Gbps são realizados à custa de estruturas em malha aberta, sendo o filtro passa banda implementado com ressonadores dieléctricos [1]. Estes elementos, não obstante terem uma excelente resposta na banda passante têm modos espúrios de ressonância fora da banda que degradam as características do sinal de relógio recuperado. Deste modo, um amplificador de banda estreita sintonizado à frequência do sinal de relógio é um elemento essencial não só para aumentar o nível do sinal, mas também para filtrar essas componentes indesejáveis. Com vista à integração de um sistema recuperador de relógio em tecnologia monolítica de Arsenieto de Gálio (GaAs MMIC) apresenta-se o projecto, simulação e desenho de dois amplificadores para utilização a 10 e 20 Gbps.

Abstract - Nowadays the clock recovery circuits used for frequencies up to 10 Gbit/s use open-loop structures. The band-pass filters used on these structures are implemented with dielectric resonators (DR). This kind of filters introduce spurious modes that degradate the characteristics of the recovered clock signal. So, the clock amplification stage is required not only to provide the desired clock signal levels, but also to reduce the magnitude of the DR filter spurious modes. Next is presented the project, simulation and design of two amplifiers (GaAs MMIC) operating at 10 and 20 Gbit/s, to be integrated in a clock recovery circuit.

## I. Introdução

Em sistemas de comunicação digitais, os recuperadores de relógio são parte importante para que possa ser efectuada uma comunicação fiável. Como tal, teremos que fazer uma escolha criteriosa do sistema de recuperação que melhor se adapta a cada caso em particular.

Para sistemas de alto débito, como é o caso em estudo (10 e 20 Gbps ), foram já realizadas experiências, baseadas em tecnologia híbrida, que comprovaram a eficiência do método de recuperação de relógio, baseado num filtro de alto Q em malha aberta [1]. O diagrama de blocos de um sistema deste tipo é constituído por um préfiltro para limitação da banda do ruído e para a melhor formatação espectral do sinal; uma não linearidade que gera, com o maior nível de sinal possível, a componente à frequência de transmissão; um filtro passa banda para

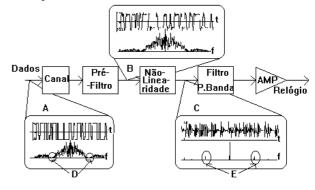

Na Fig.1 representa-se, em diagrama de blocos, o sistema recuperador de relógio em conjunto com uma representação dos sinais mais relevantes, tanto no domínio do tempo como no domínio da frequência, para o sistema recuperador de relógio em malha aberta.

Como se pode observar nessa figura (Fig.1) o espectro do sinal original (A) tem um zero à frequência de relógio (D), pelo que, só por filtragem seria impossível a sua recuperação. No entanto, após a não linearidade (C), o sinal já contém uma componente à frequência de relógio (E). Esta componente imersa em ruído é filtrada por um filtro de alto factor de qualidade (Q~700). Contudo, este filtro, implementado com um ressonador dieléctrico, apresenta, fora da banda passante principal, zonas de reduzida atenuação que degradam o sinal de relógio recuperado.

A utilização de um amplificador sintonizado à frequência do sinal de relógio permite atenuar o efeito das componentes espúrias do filtro de alto Q. Além disto, aumenta a potência do sinal recuperado para os níveis que os circuitos de decisão e desmultiplexagem necessitam.

Na secção II deste artigo é descrito o projecto, resultados de simulação e "lay-out" para o amplificador centrado a 10 GHz

Na secção III é descrito de uma forma muito abreviada o

Fig.1 - Diagrama de blocos de um sistema recuperador de relógio em malha aberta (os resultados apresentados foram obtidos da modelização do sistema descrito, na ferramenta matemática Monarch)

reduzir o nível de ruído associado à risca espectral correspondente à frequência de relógio. Finalmente, um amplificador sintonizado que pretende normalizar o nível de potência do sinal e atenuar algumas componentes de frequência indesejadas, provocados pelos modos espúrios do filtro com ressonador dieléctrico.

<sup>\*</sup>Trabalho realizado no âmbito da disciplina de Projecto

mesmo procedimento que foi tomado na secção anterior, mas agora para o amplificador centrado a 20 GHz.

#### II. AMPLIFICADOR DE BANDA ESTREITA PARA 10 GHZ.

As especificações para este amplificador são:

Gama de frequência: 9.8 a 10.8 (GHz)

Ganho:>=20 dB Ripple máximo: 1 dB

"Return Loss" à entrada <-15 dB "Return Loss" à saída < -15 dB

Como sempre o projecto de um amplificador parte do conhecimento dos parâmetros S e dos parâmetros de estabilidade do FET em causa ( FET 4X75  $\mu m$  do processo GEC-Marconi F20). Este FET revela-se particularmente instável a 10 GHz apresentando, a esta frequência, os parâmetros das Tabelas 1 e 2.

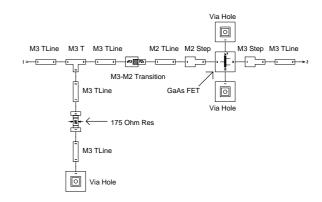

Para que o amplificador possa ser realizado, é necessário que se proceda à estabilização do dispositivo activo. Essa estabilização foi obtida por introdução de uma carga resistiva na gate do FET (R=175  $\Omega$ ), permitindo deste modo obter um novo bloco (Fig.2), que apresenta estabilidade para a banda de 1 MHz a 15 GHz.

Para que possamos continuar o desenho, necessitamos de obter explicitamente os parâmetros S e de estabilidade do bloco referido para a frequência de trabalho (10 GHz). Esses parâmetros do novo bloco encontram-se nas Tabelas 3 e 4.

Tomando agora como dispositivo activo base o bloco apresentado na Fig.2 (incondicionalmente estável) foi estudada a configuração que permitia simultaneamente a sua alimentação e adaptação para a frequência de interesse.

| S11           | S12           | S21            | S22            |

|---------------|---------------|----------------|----------------|

| 0.799∠ -95.4° | 0.097∠ 43.9 ° | 1.762∠ 100.3 ° | 0.608∠ -38.2 ° |

Tab.1 - Parâmetros S do FET em causa, a 10 GHz

| K     | Δ     | Estabilidade            |

|-------|-------|-------------------------|

| 0.686 | 0.492 | potencialmente instável |

Tab.2 - Parâmetros de estabilidade do FET em causa, a 10 GHz

| S11             | S12            | S21            | S22           |

|-----------------|----------------|----------------|---------------|

| 0.669∠ -117.3 ° | 0.071∠ 44.56 ° | 1.875∠ 98.72 ° | 0.639∠ -38.4° |

Tab.3 - Parâmetros S do bloco constituído pelo FET e a carga resistiva, a 10 GHz

| 1 |      | 1    |                            |

|---|------|------|----------------------------|

|   | K    | Δ    | Estabilidade               |

|   | 1.09 | 0.38 | incondicionalmente estável |

Tab.4 - Parâmetros de estabilidade do bloco constituído pelo FET e a carga resistiva, a 10 GHz

Fig.2 - Esquema do bloco contendo o FET estabilizado

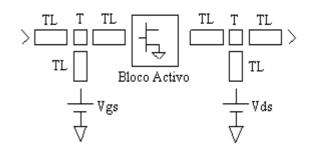

A configuração que melhor cumpriu os objectivos descritos é apresentada na Fig.3.

Com vista a tentarmos obter uma máxima robustez para o amplificador desenhado foram estudadas as respostas das malhas de polarização. O nosso objectivo é essencialmente o de obter uma malha que torne o circuito independente da resistência de saída das fontes de alimentação. O estudo que se fez, passou pela análise de estruturas que cumprissem este objectivo. A melhor configuração tem uma topologia base que é apresentada na Fig.4. Com esta configuração nas malhas de alimentação, o circuito foi simulado obtendo-se resultados bastante satisfatórios. As fontes podem ter resistências de saída com qualquer valor entre  $0.001~\Omega$  e  $10~\mathrm{M}\Omega$ , sem alterar os resultados à frequência de trabalho mais do que a segunda casa decimal de cada parâmetro S.

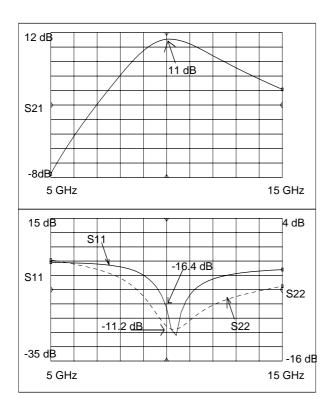

As características obtidas por simulação de um bloco com a topologia descrita na Fig.3, projectado para 10 GHz, são apresentadas na figura Fig.5.

Fig.3 - Topologia para um andar genérico ( T - Junção de 3 pontos; TL - Linha de transmissão; Vgs - Tensão Gate-Source; Vds - Tensão Dreno-Source)

Fig.4 - Diagrama esquemático de uma alimentação

Fig.5 - Resposta do 1º andar do amplificador

Como se observa obteve-se aproximadamente metade do ganho especificado para o amplificador conseguindo-se uma boa adaptação de entrada. Deste modo, necessitamos de um amplificador com 2 andares, apenas sendo de salientar o cuidado a ter na adaptação de saída para o outro andar a desenhar.

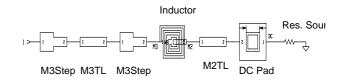

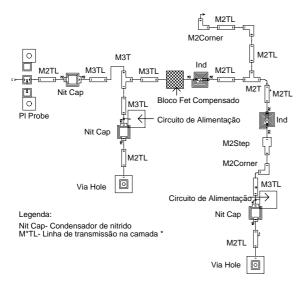

A topologia indicada na Fig.3 é a base de construção e desenho dos dois andares do amplificador final. A título de exemplo é apresentado o diagrama esquemático do 1º andar, em que são englobados já todos os componentes

Fig.6 - Diagrama esquemático do 1º andar do amplificador

Fig.7 - Amplificador final (os componentes ideais que se vêm na figura tentam simular o "bonding" de ligação da placa ao exterior; os valores do condensador - 0.0128~pF - e da bobina - 0.03~nH - são valores típicos ; quanto ao valor da segunda bobina, este foi obtido supondo que o comprimento do Bonding de ligação era de  $30~\mu m$  - como se tinha 0.7~nH/mm, a bobina assumia o valor de 0.021~nH)[2]

(Fig.6). O amplificador final tem a estrutura apresentada na Fig.7, que resultou da junção de dois andares idênticos ao especificado como 1º andar. Como é óbvio pequenos ajustes tiveram que ser efectuados, não só para que o amplificador cumprisse as especificações, mas também por imposições geométricas.

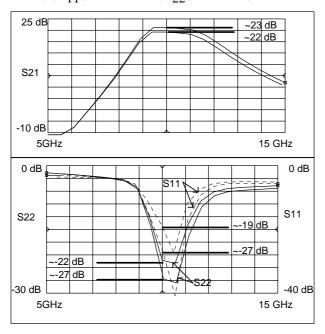

Observando a resposta final do amplificador, apresentada na Fig.8, poderemos concluir que este amplificador cumpre as especificações na sua totalidade.

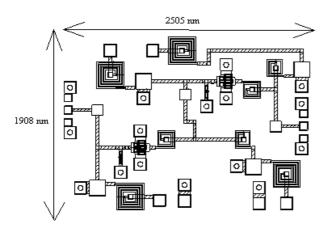

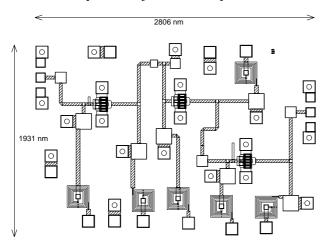

O passo seguinte na concretização do amplificador foi o desenho do "lay-out", onde se tem que levar em conta todos os pormenores de desenho em MMIC e ainda o facto de em circuitos integrados o custo ser proporcional à área utilizada. Na Fig.9 apresenta-se o aspecto do "lay-out" do amplificador final de 10 GHz, onde podemos observar que a construção do mesmo não é linear, mas sim em "Z", pois tentou-se, sem infringir nenhuma restrição de distância mínima, ocupar o mínimo espaço possível.

Fig.8 - Resposta simulada para o amplificador de 10 GHz

Fig.9 - "Lay-out" para o amplificador de 10 GHz

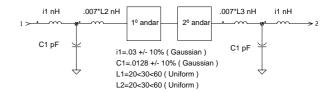

Outro factor importante no desenho de amplificadores e dispositivos electrónicos baseados em elementos com grande variância, é o teste da sua sensibilidade aos componentes que os constituem. Para isso recorremos à análise de Monte-Carlo que se encontrava disponível no programa comercial MDS-HP, em que são tomadas distribuições probabilísticas para os componentes base. Foram feitas simulações, de modo a conhecer-se a gama de valores prováveis da resposta do amplificador para as diversas excursões de cada valor de componente. As variâncias e distribuições consideradas foram baseadas nos dados que são apresentados no manual da Foundry [3].

Da observação dos gráficos (Fig.10) pode-se concluir que as tolerâncias a que estão sujeitos os vários componentes não nos vão trazer problemas. Para sustentar este facto basta repararmos que  $|S_{21}|$  é no pior caso de 22 dB,  $|S_{11}|$  de -19 dB e  $|S_{22}|$  de -22 dB, valores estes

Fig.10 - Limites dos parâmetros ( $S_{21}$ ,  $S_{11}$ ,  $S_{22}$ ) do amplificador de 10 GHz em função da tolerância dos componentes que o constituem

que se encontram ainda dentro das especificações .

#### III- O AMPLIFICADOR DE 20 GHZ

Para o amplificador de 20 GHz o projecto foi bastante mais simplificado, pois o FET (  $4X75~\mu m$  processo GEC F20 ) não apresenta instabilidade nas proximidades da frequência de trabalho (20 GHz). Seguindo os passos citados para o amplificador anterior, foi então projectado um amplificador de três andares semelhantes ao  $1^{\rm o}$  andar do amplificador de  $10~{\rm GHz}$  .

As especificações para este amplificador são idênticas às do amplificador anterior com a excepção da gama de frequências:

Gama de frequência: 19.6 a 21.6 (GHz)

Ganho : >= 20 dB Ripple máximo : 1dB

"Return Loss" à entrada < -15 dB "Return Loss" à saída < -15 dB

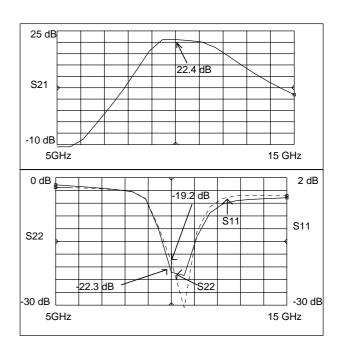

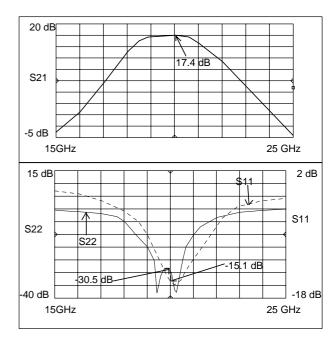

Observando a resposta final do amplificador, apresentada na Fig.11, poderemos concluir que este amplificador cumpre praticamente as especificações.

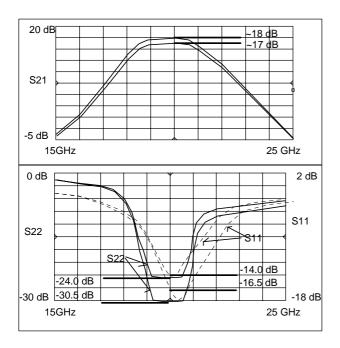

Testes de robustez foram também efectuados a este amplificador, e mais uma vez os resultados foram satisfatórios (Fig.12).

Fig.11 - Resposta do amplificador de 20 GHz

Fig.12 - Limites dos parâmetros ( $S_{21}$  , $S_{11}$  , $S_{22}$  ) do amplificador de 20 GHz em função da tolerância dos componentes que o constituem

Podemos ver na Fig.12 que o ganho é sempre superior a 17 dB, a adaptação de entrada é sempre inferior a -14 dB e a adaptação de saída inferior a -24 dB, cumprindo praticamente as especificações.

O seu "lay-out" tem o aspecto apresentado na Fig.13, e como se vê há novamente uma grande densidade de componentes, sempre com vista a minimizar o espaço ocupado, que por comparação com o amplificador anterior, e sabendo que este contém mais um andar, se apresenta bastante mais comprimido.

## IV- CONCLUSÃO

Apresentaram-se os projectos de dois amplificadores em tecnologia monolítica de Arsenieto de Gálio. Estes amplificadores apresentam para 10 e 20 GHz um ganho suficiente, de forma a que o nível do sinal nos circuitos de decisão subsequentes seja suficiente para um correcto

Fig.13 - "Lay-out" para o amplificador de 20 Ghz

processamento. Além disso, apresentam uma resposta fora da banda de passagem que leva a que as componentes espúrias presentes à saída do filtro sejam eliminadas. Pode-se então concluir que os amplificadores finais obedecem às especificações que nos propusemos atingir.

### REFERÊNCIAS

- [1] P.Monteiro, J.N.Matos, A.Gameiro and J.R.F. da Rocha, "10Gbps timing recovery circuit using dielectric resonator and active bandpass filters", Electronic Letters, 23 rd April 1992, v.28, n.9

- [2] "GaAs IC Foundry Design Manual" pág.7-8, cap.7.3 Die Interface Parameters TF/HF/00001/000

- [3] "GaAs IC Foundry Design Manual" ,TF/HF/00001/000.