# Receptor Digital para Medição de Balizas de Satélite

Jorge André Pires, Ricardo Sousa, Armando Rocha

Resumo - Neste artigo é apresentado o protótipo de um receptor digital para medição da amplitude de balizas de satélite destinado a campanhas experimentais de propagação Terra-Satélite. O sinal é digitalizado em HF por uma ADC operando a 40Ms/s e seguidamente convertido em frequência e decimado por um chip numérico. As amostras são transferidas para um kit DSP que implementa uma malha de sincronismo de fase (PLL) por software programando o oscilador de controlo numérico do chip (NCO). São apresentados alguns resultados com o sistema a operar em malha fechada e discutidas hipóteses de trabalho futuro.

Abstract - A prototype for a digital beacon receiver to be used in Earth-Satellite propagation experiments is presented. The HF signal is sampled at about 40Ms/s using a high speed ADC, down converted and decimated by a signal processing chip. The output samples are processed by a DSP development kit that implements phase locked loop by software. The VCO is implemented by reprogramming the chip numerical oscillator (NCO). Preliminary results are presented for closed loop operation and several starting conditions. Future work topics are discussed.

## I. INTRODUÇÃO

Sistemas de telecomunicações por satélite usando frequências acima de 10GHz estão sujeitos à degradação de sinal devido a fenómenos de atenuação, despolarização e cintilação causados por factores atmosféricos tais como chuva, nuvens e irregularidades de humidade e temperatura. Enquanto para a banda Ku era possível implementar sistemas com margens de atenuação para oferecer disponibilidade de serviço para 99.99% tal não é possível a frequências superiores pois a atenuação agravase. A utilização de técnicas de mitigação da atenuação (FMT's) é então imprescindível e o seu adequado dimensionamento exige modelos realistas do canal.

O desenvolvimento destes modelos do comportamento estático e dinâmico do canal de propagação recomenda campanhas experimentais como a monitorização da amplitude de um sinal de frequência fixa (denominado baliza) emitido por um satélite.

Para medição de atenuação monitoriza-se o sinal com a mesma polarização do sinal enviado (copolar) e eventualmente, para estudos de despolarização, também a amplitude e a fase relativa do sinal com polarização ortogonal (crosspolar).

O receptor de propagação é o equipamento que permite medir com elevada sensibilidade estes sinais a uma cadência típica de 1 a 10 amostras por segundo. Trata-se de um receptor super-heterodino constituído por uma antena parabólica, uma unidade exterior para préamplificação/conversão do sinal, uma unidade interior com outros estágios de conversão e circuitos de sincronismo e detecção. Elevada estabilidade, linearidade e sensibilidade são requisitos difíceis de conseguir num sistema que terá ganho superior a 100dB repartido por três ou quatro frequências intermédias (FI's).

### II. A PROBLEMÁTICA DA MEDIÇÃO DE UMA BALIZA

O sinal a detectar poderá ser descrito pela Eq. (1) e pretende-se medir A(t) ou a respectiva potência  $A^2(t)$ .

$$s(t) = A(t)\sin(\omega_0 t + \phi(t)) + n(t). \tag{1}$$

Contudo esta medição é um problema pouco trivial pois:

- O sinal é acompanhado por ruído branco gaussiano n(t). A densidade espectral da relação Sinal/Ruído (CNR) é menor ou igual 55dB/Hz.

- O ruído de fase, representado pelo processo aleatório  $\phi(t)$ , distribui a potência do sinal numa largura de banda da ordem de 50Hz.

- A frequência ω<sub>0</sub> pode variar, embora de forma lenta, cerca de 2-3kHz por dia.

A detecção síncrona é recomendável mas exige a implementação de uma malha que sincronize o sinal com um oscilador local (normalmente um oscilador a cristal controlado por tensão VCXO). Uma vez obtidas as componentes em fase e quadratura (I/Q) no detector síncrono é fácil calcular a amplitude do sinal e sua fase relativa em relação à referência. É comum usar uma malha de sincronismo de fase (PLL) mas outras abordagens prometem uma maior gama dinâmica embora a fase relativa num receptor de dois canais se possa perder para baixas CNR.

#### III. RECEPTOR DIGITAL VERSUS ANALÓGICO

A detecção de fase numa PLL analógica é implementada numa FI de alguns MHz ou dezenas de KHz. O VCXO deve operar a alguns MHz para conseguir um desvio de frequência suficiente. Isto exige complexidade na síntese

de osciladores locais, o desenvolvimento de uma ou duas FI's na unidade interior e circuitos de sincronização complexos. O hardware analógico não dispensa também ajustes periódicos e é dificilmente reconfigurável.

A gestão do sincronismo é problemática. Quando o sinal se atenua a CNR degrada-se e a PLL pode perder o sincronismo: a aquisição terá que ser forçada e pode levar algumas dezenas de segundos a efectuar-se. Circuitos para detecção de sincronismo e auxílio à sincronização são delicados de projectar e ajustar. Do ponto de vista experimental a perda de períodos importantes de dados (atenuação significativa) é quase inevitável.

É hoje em dia possível encontrar no mercado ADC's com taxas de amostragem de dezenas de MS/s (12bits) e chips programáveis DRSP (Digital Receiver Signal Processor) compreendendo a conversão digital de frequência (DDC), osciladores de controlo numérico (NCO) e estágios decimadores.

Ao digitalizar o sinal numa FI de alguns MHz e implementar o receptor no domínio digital poderemos:

- Melhorar a linearidade, estabilidade e fiabilidade;

- Reduzir os custos de desenvolvimento;

- Obter flexibilidade acrescida: larguras de banda ajustáveis, liberdade na escolha da FI que facilita opções no hardware analógico a montante, etc;

- Gerir com inteligência a malha de sincronismo, mesmo quando esta enfrenta condições adversas, pelo uso de técnicas de processamento de sinal.

## IV. IMPLEMENTAÇÃO DO RECEPTOR DIGITAL

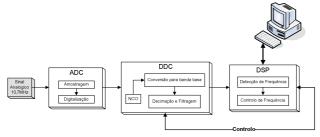

O diagrama de blocos descrito na Fig. 1 ilustra a aproximação proposta neste trabalho. Como sinal de entrada temos uma FI que, sem grande perda de generalidade, iremos assumir a 10.7MHz. Este é um valor standard e para o qual existe uma maior disponibilidade de componentes analógicos.

Fig. 1 – Diagrama de blocos funcional do receptor.

O processamento do sinal no receptor digital divide-se pelas seguintes etapas:

- Amostragem e digitalização do sinal numa FI;

- Estágio de processamento com o DRSP;

- Processamento digital do sinal num DSP.

Desenvolveu-se uma placa com interface a uma DSP, cujos componentes principais são uma ADC e um DRSP. O NCO tem saídas de 0 e 90°, dois multiplicadores numéricos funcionando como conversores de frequência digital e 3 filtros decimadores em cascata. As amostras são transferidas para um dispositivo programável (DSP), no âmbito do qual poderão ser implementadas rotinas de seguimento uma vez que a frequência do NCO é programável em tempo real.

A abordagem em termos de hardware é idêntica à encontrada em [1], mas no nosso caso implementou-se uma malha de seguimento para implementar a detecção síncrona.

### A. Processamento Digital por Hardware

O sinal a adquirir, embora possua uma largura de banda muito reduzida, é amostrado a Super-Nyquist por uma ADC da *Analog Devices*: o AD6640 com 12 bits de resolução. A taxa de aquisição máxima é de 65MS/s mas foi usada uma taxa de 40MS/s recorrendo a um oscilador a cristal (clock) que é partilhado com o DRSP. A interface entre os circuitos é directa pois usam uma lógica de 3.3V.

O chip DRSP (AD6620), também da *Analog Devices*, multiplica as amostras em dois multiplicadores independentes pelas componentes em fase e quadratura do NCO. As saídas dos multiplicadores são sujeitas a dois estágios de decimação (CIC2 e CIC5) de coeficientes fixos mas com factores de divisão programáveis. Um 3º estágio final, também com factor de divisão programável (RCF), é efectuado por um filtro FIR cujos coeficientes poderão ser programados.

Os dados de saída (componentes I/Q) são transferidos por uma interface paralela ou série. A porta paralela oferece maior velocidade mas os dados têm uma resolução máxima de 16 bits. O chip oferece ainda a possibilidade de sincronizar a transferência de dados série com outro chip escravo permitindo a fácil expansão do hardware.

# B. Aquisição e Seguimento do Sinal

O processamento digital dos dados estará a cargo de uma DSP TMS320C6711 da *Texas Instruments* num kit de desenvolvimento DSKC6711, que permitirá implementar todos os algoritmos necessários incluindo a programação em tempo real do NCO do AD6620.

A abordagem tomada neste projecto foi mapear os registos de programação do AD6620 num dos espaços de memória EMIF (External Memory Interface) da DSP para um acesso assíncrono. A leitura e escrita (programação) em tempo real são assim facilitadas pois o clock da placa e da DSP não são síncronos.

A transferência de dados é efectuada pela porta série McBSP mas é iniciada pelo AD6620 e cadenciada com base do clock da placa desenvolvida.

#### V. PROJECTO DA PLL

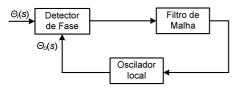

Uma PLL é um sistema com realimentação constituído por três elementos essenciais constantes da Fig. 2: detector de fase, um filtro de malha e um oscilador local.

Fig. 2 – Diagrama de blocos de uma PLL.

O objectivo da PLL é igualar as frequências do sinal e do oscilador local desenvolvendo uma diferença de fase que corrija o oscilador local.

## A. PLL analógica

O filtro de malha mais utilizado é activo e possui um integrador perfeito. A função de transferência da malha é dada, nestas circunstâncias, por:

$$H(s) = \frac{\theta_i(s)}{\theta_0(s)} = \frac{2\zeta\omega_n s + 1}{s^2 + 2\zeta\omega_n s + 1},$$

(2)

onde  $\theta_i(s)$  e  $\theta_o(s)$  são as fases do sinal de entrada e do VCO,  $\zeta$  a constante de amortecimento e  $\omega_n$  a frequência natural.

Conhecidas as constantes do detector de fase  $K_d$  (V/rad) e do VCO  $K_0$  (Hz/V), temos as seguintes relações:

$$\tau_{1} = \frac{K_{0}K_{d}}{\omega_{n}^{2}},$$

$$\tau_{2} = 2\zeta\sqrt{\frac{\tau_{1}}{K_{0}K_{d}}},$$

$$B_{L} = \frac{\omega_{n}}{2}\left(\zeta + \frac{1}{4\zeta}\right).$$

(3)

$B_L$  é a denominada largura de banda de ruído da PLL,  $\tau_I$  e  $\tau_2$  são constantes de tempo do filtro. A largura de banda de ruído recomendável é da ordem de 50Hz. Um valor superior de  $B_L$  permite seguir uma fracção maior da potência do sinal mas admite maior potência de ruído na malha degradando a qualidade do sincronismo. A constante de amortecimento deve ser  $\zeta$ =0.707 ou ligeiramente menor.

Nestas aplicações é aceitável uma SNR de 10dB na malha da PLL. Teremos uma gama dinâmica para a medida de atenuação de 28dB para uma CNR de 55dB/Hz.

## B. PLL – Digital

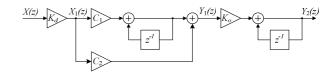

Para a implementação da PLL digital pretende-se obter uma resposta em frequência semelhante à resposta da PLL analógica. O filtro digital da malha será implementado pela DSP, o NCO desempenha o papel de VCO e o DDC será o detector de fase.

O diagrama de blocos em malha aberta, Fig. 3, ilustra o sistema implementado e inclui os ganhos do detector de fase e do NCO ( $K_d$  e  $K_o$ ). O último bloco representa o efeito integrador do VCO sobre a fase.

Fig. 3 - Diagrama de blocos em malha aberta: PLL digital.

O filtro de malha consiste num integrador de ganho  $C_1$ , a cuja saída é somada ainda uma contribuição proporcional de ganho  $C_2$ .

A função de transferência filtro digital é dada por:

$$\frac{Y_1(z)}{X_1(z)} = \frac{C_1}{1 - z^{-1}} + C_2, \tag{4}$$

onde  $X_I(z)$  é a componente em quadratura entregue à DSP.

A função de transferência em malha aberta vem agora dada por:

$$\frac{Y_2(z)}{X(z)} = K_d K_o \cdot \left(\frac{C_1}{1 - z^{-1}} + C_2\right) \cdot \frac{1}{1 - z^{-1}}.$$

(5)

Por fim, a função de transferência em malha fechada da PLL digital é dada por:

$$H(z) = \frac{Y(z)}{X(z)} = \frac{K_d K_o \cdot \left(\frac{C_1}{1 - z^{-1}} + C_2\right) \cdot \frac{1}{1 - z^{-1}}}{1 + K_d K_o \cdot \left(\frac{C_1}{1 - z^{-1}} + C_2\right) \cdot \frac{1}{1 - z^{-1}}}.$$

(6)

Repare-se que este modelo não inclui o efeito dos filtros CIC e RCF nem o impacto do atraso previsível de uma amostra na programação do NCO em tempo real. Uma análise preliminar nas condições de funcionamento mostra que a margem de fase não é comprometida.

Os valores  $C_1$  e  $C_2$  são dimensionados por analogia com a PLL analógica. Para o efeito usou-se a transformação entre o domínio S e Z (s << T) da equação:

$$z^{-1} = 1 - sT \,. \tag{7}$$

onde T representa período de amostragem. Substituindo a Eq. (7) na Eq. (4), obtém-se a função de transferência da PLL digital:

$$H(s) = \frac{K_d K_o \cdot \left(\frac{C_1}{sT} + C_2\right) \cdot \frac{1}{sT}}{1 + K_d K_o \cdot \left(\frac{C_1}{sT} + C_2\right) \cdot \frac{1}{sT}}.$$

(8)

# C. Dimensionamento da PLL Digital

O ganho do detector de fase foi calculado usando os dados adquiridos para um sinal com uma potência de 0dBm e o seu valor é dado por:

$$K_d = 2^{14.23}$$

[Unidade/Rad]. (9)

O ganho do NCO corresponde à resolução em frequência deste oscilador (acumulador de 32 bits) e é dado por:

$$K_0 = \Delta f_{NCO} = 9.313x10^{-3}$$

[Hz/Unidade]. (10)

Assumindo os valores de  $B_L = 50$ Hz e  $\zeta = 0.707$ , recorrendo às relações descritas em (3), determinaram-se as constantes de tempo  $\tau_1$  e  $\tau_2$ :

$$\tau_1 = 14.91 \text{ [}\mu\text{s]}.$$

(11)

$$\tau_2 = 15.0 \text{ [ms]}.$$

(12)

Sabendo que o período de amostragem *T* é de cerca de 0.2048ms, determinaram-se as constantes do filtro digital:

$$C_1 = \frac{T^2}{\tau_1} \Box 0.0028 \quad [s],$$

(13)

$$C_2 = T \frac{\tau_2}{\tau_1} \square 0.206 \text{ [s]}.$$

(14)

Assim, numa primeira aproximação, a função de transferência da PLL digital é dada por:

$$H(z) = \frac{-0.0273 \cdot z^{-1} + 0.0277}{z^{-2} - 2.0273 \cdot z^{-1} + 1.0277}.$$

(15)

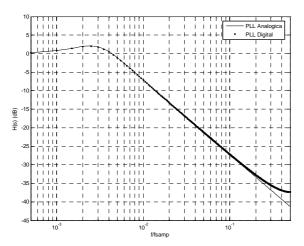

Fig. 4 – Função de transferência da PLL analógica – H(s) e da PLL digital – H(z).

Na Fig. 4, está representada a resposta em amplitude da PLL analógica e a resposta "equivalente" para a PLL digital. Naturalmente, a função H(z) repetir-se-á a partir da metade da frequência de amostragem.

### VI. IMPLEMENTAÇÃO DO HARDWARE

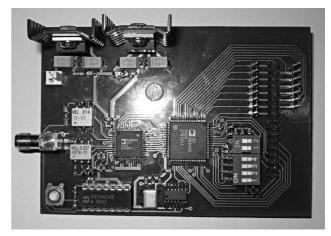

Foi desenhada uma placa em circuito impresso e mandada executar em furo metalizado. A montagem dos componentes da placa principal foi estruturada em algumas etapas, intermediadas por alguns testes de hardware para prevenir erros fatais de alimentação nos componentes principais.

Fig. 5 – Aspecto da placa desenvolvida: conector de interface por baixo da placa.

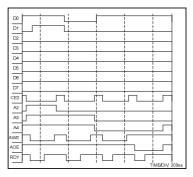

A primeira série de testes visou operacionalizar a comunicação bidireccional EMIF-AD6620 para efectuar a programação e configuração deste chip. Os testes foram considerados terminados após confirmar que os dados lidos da memória interna do chip coincidiam com os programados. O analisador lógico foi a ferramenta mais útil (a Fig. 6 mostra um episódio crucial nos testes) para ajudar a detectar não só erros de hardware mas também de configuração da EMIF.

Fig. 6 – Ciclo de escrita, seguido de leitura, num registo interno do AD6620.

Depois de corrigidos alguns problemas menores de software e hardware, passou a ser possível activar a porta série do AD6620.

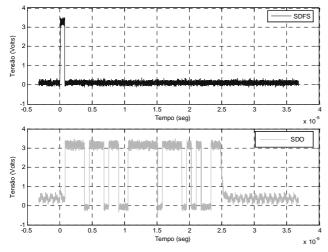

O passo seguinte focou o teste de software e de hardware para a comunicação série com o AD6620. Recorreu-se ao analisador lógico e posteriormente a um osciloscópio digital de sampling, para observar os sinais nos pinos relativos ao envio de dados pela porta série (Fig. 7).

Fig. 7 – Teste da Porta Série: Pinos SDFS (Serial Data Frame Start) e SDO (Serial Data Out).

Depois de terminados os testes, tinha-se um sistema completamente funcional e pronto a ser utilizado para a realização de todas as tarefas implicadas neste projecto.

#### VII. SOFTWARE

O software desenvolvido em linguagem C, usando o Code Composer Studio, passou por duas fases:

- Configuração básica do sistema com vista à resolução de problemas de hardware/software com apoio do analisador lógico;

- Implementação de rotinas necessárias à realização de uma malha PLL por software.

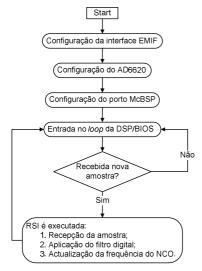

Fig. 8 – Flowchart: programação do sistema e implementação da PLL por software.

No diagrama de fluxo da Fig. 8, estão representados os principais passos da programação respeitante já à implementação da PLL digital:

• Programação dos parâmetros da EMIF [2]: endianess, tipo de acesso, ciclos de clock de acesso, etc.

- Programação do AD6620: factores de divisão CIC, FIR, coeficientes de filtro FIR, ganhos, NCO, etc.

- Programação da Porta Série (McBSP): Número de bits, origem do clock, aspectos de sincronização, etc.

- Configuração e rotina de serviço ao interrupt desencadeado pela recepção de uma amostra I/Q na porta série, cálculos do filtro digital e actualização da frequência do NCO.

Embora tenha sido aqui implementada uma PLL outras soluções poderão vir a ser testadas para a malha tais como AFC (Automatic Frequency Control) usando como detector de frequência uma FFT ou correlador cruzado[3]. Eventualmente uma PLL a operar até uma SNR na malha de 10dB e uma AFC para sinais mais fracos poderá ser uma boa solução.

O que importa realçar é a abertura de enormes capacidades de processamento de sinal que se apresentam passando as tarefas para uma DSP e implementando meras rotinas.

# VIII. RESULTADOS

Os factores de divisão e o ganho dos estágios decimadores do chip foram optimizados para máxima gama dinâmica sem risco de overflow/underflow dos acumuladores internos.

O filtro FIR foi dimensionado para uma frequência de corte de 1kHz (>>50Hz). A versão actual do software prevê a transferência de dados a uma taxa de cerca de 4KS/s a qual garante um atraso relativamente pequeno na correcção da frequência. A transferência dos dados pode no entanto alcançar os 160kS/s pela porta série.

## A. Testes em Malha Aberta

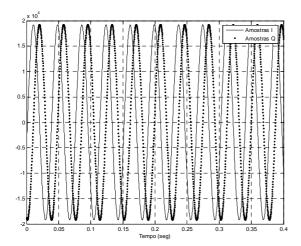

Na Fig. 9, estão representadas as primeiras séries temporais resultantes da aquisição de um sinal de entrada com um gerador de RF a 10.70001MHz e com o NCO configurado para 10.7MHz.

As amostras I e Q correspondem a duas sinusóides com a mesma amplitude mas com uma diferença de fase exacta de 90°. A frequência não coincide aritmeticamente com a diferença de frequências do NCO e do gerador. Isto devese ao facto do oscilador de cristal da placa (clock) e o sinal do gerador serem osciladores independentes.

Estes resultados permitiram comprovar que, por um lado, o *chip* AD6620 estava a ser configurado correctamente e por outro lado, que a DSP recebia correctamente os dados enviados.

Fig. 9 – Série temporal: Amostras I e Q

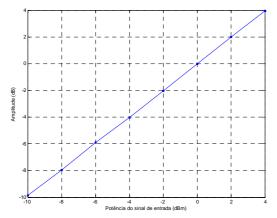

Na Fig. 10, estão representados os resultados de um teste muito limitado de linearidade: compreende apenas 14dB. Num sistema em malha fechada são indispensáveis testes rigorosos pelo menos numa gama dinâmica correspondente ao adequado funcionamento da PLL: no exemplo dado seria 28dB.

Fig. 10 – Amplitude medida versus amplitude configurada no gerador.

# B. Testes em Malha Fechada

Estes são os resultados mais interessantes, quasi didáticos, e que mostram o sucesso da implementação e o desempenho da PLL digital.

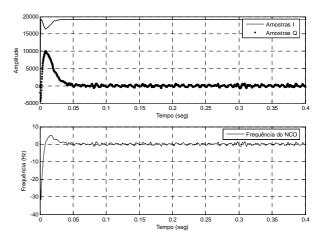

Escolheu-se uma frequência inicial para o NCO de  $f_{NCO}$  = 10.7MHz e optou-se por receber 2000 amostras (cerca de 0.4s de dados) para as componentes I e Q e também os valores de frequência configurados no NCO.

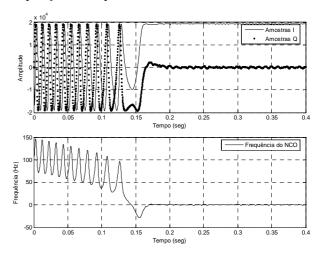

Os resultados apresentados na Fig. 11 e Fig. 12 mostram o processo de aquisição para diferentes desvios iniciais,  $\Delta f$ , da frequência do sinal de entrada em relação ao valor inicialmente programado no NCO. De notar que a frequência apresentada nos gráficos é a diferença entre a frequência programada no NCO e o valor médio desta após a aquisição estar concluída.

Dado que o filtro da malha tem um integrador perfeito o denominador comum nas figuras é, após sincronismo ou seja quando a frequência no NCO iguala a frequência do sinal de entrada, uma componente Q com média nula. A componente I (DC obviamente) será a amplitude do sinal de entrada.

Fig. 11 – Amostras I e Q e variação de frequência no NCO, com Δf ~20Hz.

Na Fig. 11 o sincronismo ocorre muito rapidamente. A mistura do sinal com o NCO tem frequência baixa pelo que a componente em quadratura (saída do detector de fase) é integrada rapidamente para anular o erro de fase.

Tal não é o caso apresentado na Fig. 12. A diferença de frequências inicial dá origem a um batimento que, embora parecendo sinusoidal, possui uma componente DC devido à modulação residual do NCO. Esta débil componente DC é integrada pelo filtro, aumenta de amplitude e o processo de aquisição acaba por ter sucesso ao fim de cerca 180ms.

Fig. 12 – Amostras I e Q e variação de frequência no NCO, com  $\Delta f \sim 120$ Hz.

Para diferenças de frequência bastante superiores a estes valores as observações efectuadas indiciam que a PLL conseguirá o sincronismo (frequência do NCO aproximase) mas tal não ocorreu no curto período de tempo da observação de 400ms. A aquisição será pouco provável

para uma diferença superior à largura de banda do filtro FIR (1kHz). O processo de aquisição depende das características da PLL e será de certeza mais problemático na presença de ruído. Este assunto é abordado com rigor na literatura [4, 5].

Recorrendo às séries temporais da frequência programada no NCO estimou-se uma variância de fase residual de  $\sigma_{\theta_0}^2=4.05*10^{-7}\,rad^2$ . Este valor é equivalente ao provocado por ruído aditivo gaussiano com SNR~60dB. As contribuições residuais podem ser devidas ao ruído de fase do gerador de RF (pior que um oscilador a cristal devido aos circuitos de síntese internos, mas melhor que o da baliza), do clock da placa e ainda dos patamares de ruído do AD6620 e do gerador.

O desempenho preliminar do sistema é portanto muito bom e totalmente encorajante.

#### IX. TRABALHO FUTURO

Existe ainda algum trabalho, tanto na área de software como de hardware, que necessita de ser desenvolvido. Na área de software:

- Implementação de software para controlo automático de ganho (AGC) é absolutamente necessária para manter as constantes da malha PLL se o sinal se atenuar. A largura de banda do AGC e a forma de estimar a amplitude (coerente ou não) devem ser avaliadas.

- Filtragem das componentes cartesianas para uma taxa de amostragem final de cerca de 10Hz.

- Transferência das componentes cartesianas para o PC anfitrião em tempo real.

- Estudar políticas para administrar a degradação da CNR e que favoreçam a imediata recuperação do sincronismo. Congelar/limitar a frequência do NCO, utilizar uma malha auxiliar com AFC, uso de FFT's são algumas hipóteses.

- Desenvolver algoritmo, similar ao sugerido em [1], para efectuar a aquisição num curto espaço de tempo na situação Switch-On pelo menos.

Do ponto de vista de hardware e de sistema:

- Simulação usando um sinal com relação CNR realista;

- Teste do sistema com sinal realista: ruído aditivo, variação dinâmica de amplitude, avaliação da linearidade, gama dinâmica, etc;

- Desenvolvimento de uma versão de dois canais: copolar e crosspolar.

A importação dos dados para a avaliação do desempenho do sistema foi uma tarefa muito trabalhosa e demorada. Algum investimento na utilização do "Link for Code Composer Studio" do MatLab poderá trazer, neste âmbito,

razoáveis benefícios em futuros desenvolvimentos de software.

#### X. REFERENCES

- Cornelis, J.K., B. BowThorpe, and O.J. Teong. A DSP Based Satellite Beacon Receiver and Radiometer. in Asia-Pacific Microwave Conference. 1998. Sydney, Australia.

- Texas-Instruments. TMS320C6000 DSP External Memory Interface (EMIF) Reference Guide. 2005

- Natali, F.D., AFC Tracking Algorithms. IEEE Transactions on Communications, 1984. COM-32(8): p. 935-947.

- 4. Blanchard, A., Phase-Locked Loops Application to Coherent Receiver Design. 1976: John Wiley & Sons.

- Gardner, F.M., Phaselock Techniques, ed. J.W. Sons. 1966, New York.